# THE ART OF COMPUTER PROGRAMMING

**FASCICLE 1**

# **MMIX**

DONALD E. KNUTH Stanford University

ADDISON-WESLEY

Internet page http://www-cs-faculty.stanford.edu/~knuth/taocp.html contains current information about this book and related books.

See also http://www-cs-faculty.stanford.edu/~knuth/mmix.html for downloadable software, and http://mmixmasters.sourceforge.net for general news about MMIX.

Copyright © 1999 by Addison-Wesley

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior consent of the publisher, except that the official electronic file may be used to print single copies for personal (not commercial) use.

Zeroth printing (revision 15), 15 February 2004

# **PREFACE**

```

fas·ci·cle \'fasəkəl\ n ... 1: a small bundle ... an inflorescence consisting of a compacted cyme less capitate than a glomerule ... 2: one of the divisions of a book published in parts

— P. B. GOVE, Webster's Third New International Dictionary (1961)

```

This is the first of a series of updates that I plan to make available at regular intervals as I continue working toward the ultimate editions of *The Art of Computer Programming*.

I was inspired to prepare fascicles like this by the example of Charles Dickens, who issued his novels in serial form; he published a dozen installments of *Oliver Twist* before having any idea what would become of Bill Sikes! I was thinking also of James Murray, who began to publish 350-page portions of the Oxford English Dictionary in 1884, finishing the letter B in 1888 and the letter C in 1895. (Murray died in 1915 while working on the letter T; my task is, fortunately, much simpler than his.)

Unlike Dickens and Murray, I have computers to help me edit the material, so that I can easily make changes before putting everything together in its final form. Although I'm trying my best to write comprehensive accounts that need no further revision, I know that every page brings me hundreds of opportunities to make mistakes and to miss important ideas. My files are bursting with notes about beautiful algorithms that have been discovered, but computer science has grown to the point where I cannot hope to be an authority on all the material I wish to cover. Therefore I need extensive feedback from readers before I can finalize the official volumes.

In other words, I think these fascicles will contain a lot of Good Stuff, and I'm excited about the opportunity to present everything I write to whoever wants to read it, but I also expect that beta-testers like you can help me make it Way Better. As usual, I will gratefully pay a reward of \$2.56 to the first person who reports anything that is technically, historically, typographically, or politically incorrect.

Charles Dickens usually published his work once a month, sometimes once a week; James Murray tended to finish a 350-page installment about once every 18 months. My goal, God willing, is to produce two 128-page fascicles per year. Most of the fascicles will represent new material destined for Volumes 4 and higher; but sometimes I will be presenting amendments to one or more of the earlier volumes. For example, Volume 4 will need to refer to topics that belong in Volume 3, but weren't invented when Volume 3 first came out. With luck, the entire work will make sense eventually.

#### iv PREFACE

Fascicle Number One is about MMIX, the long-promised replacement for MIX. Thirty years have passed since the MIX computer was designed, and computer architecture has been converging during those years towards a rather different style of machine. Therefore I decided in 1990 to replace MIX with a new computer that would contain even less saturated fat than its predecessor.

Exercise 1.3.1–25 in the first three editions of Volume 1 spoke of an extended MIX called MixMaster, which was upward compatible with the old version. But MixMaster itself has long been hopelessly obsolete. It allowed for several gigabytes of memory, but one couldn't even use it with ASCII code to print lowercase letters. And ouch, its standard subroutine calling convention was irrevocably based on self-modifying instructions! Decimal arithmetic and self-modifying code were popular in 1962, but they sure have disappeared quickly as machines have gotten bigger and faster. Fortunately the new RISC machines have a very appealing structure, so I've had a chance to design a new computer that is not only up to date but also fun.

Many readers are no doubt thinking, "Why does Knuth replace MIX by another machine instead of just sticking to a high-level programming language? Hardly anybody uses assemblers these days." Such people are entitled to their opinions, and they need not bother reading the machine-language parts of my books. But the reasons for machine language that I gave in the preface to Volume 1, written in the early 1960s, remain valid today:

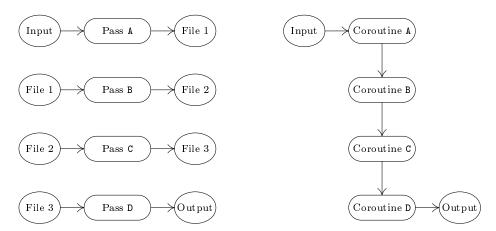

- One of the principal goals of my books is to show how high-level constructions are actually implemented in machines, not simply to show how they are applied. I explain coroutine linkage, tree structures, random number generation, high-precision arithmetic, radix conversion, packing of data, combinatorial searching, recursion, etc., from the ground up.

- The programs needed in my books are generally so short that their main points can be grasped easily.

- People who are more than casually interested in computers should have at least some idea of what the underlying hardware is like. Otherwise the programs they write will be pretty weird.

- Machine language is necessary in any case, as output of some of the software that I describe.

- Expressing basic methods like algorithms for sorting and searching in machine language makes it possible to carry out meaningful studies of the effects of cache and RAM size and other hardware characteristics (memory speed, pipelining, multiple issue, lookaside buffers, the size of cache blocks, etc.) when comparing different schemes.

Moreover, if I did use a high-level language, what language should it be? In the 1960s I would probably have chosen Algol W; in the 1970s, I would then have had to rewrite my books using Pascal; in the 1980s, I would surely have changed everything to C; in the 1990s, I would have had to switch to C++ and then probably to Java. In the 2000s, yet another language will no doubt be de

rigueur. I cannot afford the time to rewrite my books as languages go in and out of fashion; languages aren't the point of my books, the point is rather what you can do in your favorite language. My books focus on timeless truths.

Therefore I will continue to use English as the high-level language in *The Art of Computer Programming*, and I will continue to use a low-level language to indicate how machines actually compute. Readers who only want to see algorithms that are already packaged in a plug-in way, using a trendy language, should buy other people's books.

The good news is that programming for  ${\tt MMIX}$  is pleasant and simple. This fascicle presents

- 1) a programmer's introduction to the machine (replacing Section 1.3.1 of Volume 1);

- 2) the MMIX assembly language (replacing Section 1.3.2);

- 3) new material on subroutines, coroutines, and interpretive routines (replacing Sections 1.4.1, 1.4.2, and 1.4.3).

Of course, MIX appears in many places throughout Volumes 1-3, and dozens of programs need to be rewritten for MMIX. Readers who would like to help with this conversion process are encouraged to join the MMIXmasters, a happy group of volunteers based at mmixmasters.sourceforge.net.

I am extremely grateful to all the people who helped me with the design of MMIX. In particular, John Hennessy and Richard L. Sites deserve special thanks for their active participation and substantial contributions. Thanks also to Vladimir Ivanović for volunteering to be the MMIX grandmaster/webmaster.

Stanford, California May 1999

D. E. K.

You can, if you want, rewrite forever.

— NEIL SIMON, Rewrites: A Memoir (1996)

# **CONTENTS**

| Chapter 1 — Basic Concepts                    | 1   |

|-----------------------------------------------|-----|

| 1.3'. MMIX                                    | 2   |

| 1.3.1'. Description of MMIX                   | 2   |

| 1.3.2'. The MMIX Assembly Language            | 28  |

| 1.4'. Some Fundamental Programming Techniques | 52  |

| 1.4.1'. Subroutines                           | 52  |

| 1.4.2'. Coroutines                            | 66  |

| 1.4.3'. Interpretive Routines                 | 73  |

| Answers to Exercises                          | 94  |

| Index and Glossary                            | 127 |

#### 1.3′ MMIX

IN MANY PLACES throughout this book we will have occasion to refer to a computer's internal machine language. The machine we use is a mythical computer called "MMIX." MMIX—pronounced *EM-micks*—is very much like nearly every general-purpose computer designed since 1985, except that it is, perhaps, nicer. The language of MMIX is powerful enough to allow brief programs to be written for most algorithms, yet simple enough so that its operations are easily learned.

The reader is urged to study this section carefully, since MMIX language appears in so many parts of this book. There should be no hesitation about learning a machine language; indeed, the author once found it not uncommon to be writing programs in a half dozen different machine languages during the same week! Everyone with more than a casual interest in computers will probably get to know at least one machine language sooner or later. Machine language helps programmers understand what really goes on inside their computers. And once one machine language has been learned, the characteristics of another are easy to assimilate. Computer science is largely concerned with an understanding of how low-level details make it possible to achieve high-level goals.

Software for running MMIX programs on almost any real computer can be downloaded from the website for this book (see page ii). The complete source code for the author's MMIX routines appears in the book MMIXware [Lecture Notes in Computer Science 1750 (1999)]; that book will be called "the MMIXware document" in the following pages.

# 1.3.1'. Description of MMIX

MMIX is a polyunsaturated, 100% natural computer. Like most machines, it has an identifying number—the 2009. This number was found by taking 14 actual computers very similar to MMIX and on which MMIX could easily be simulated, then averaging their numbers with equal weight:

```

\begin{aligned} & \text{(Cray I + IBM 801 + RISC II + Clipper C300 + AMD 29K + Motorola 88K}} \\ & + \text{IBM 601 + Intel i960 + Alpha 21164 + POWER 2 + MIPS R4000} \\ & + \text{Hitachi SuperH4 + StrongARM 110 + Sparc 64)/14} \\ &= 28126/14 = 2009. \end{aligned}

```

The same number may also be obtained in a simpler way by taking Roman numerals.

**Bits and bytes.** MMIX works with patterns of 0s and 1s, commonly called binary digits or *bits*, and it usually deals with 64 bits at a time. For example, the 64-bit quantity

is a typical pattern that the machine might encounter. Long patterns like this can be expressed more conveniently if we group the bits four at a time and use

hexadecimal digits to represent each group. The sixteen hexadecimal digits are

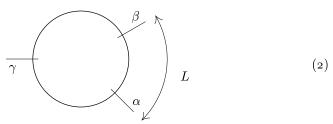

We shall always use a distinctive typeface for hexadecimal digits, as shown here, so that they won't be confused with the decimal digits 0–9; and we will usually also put the symbol # just before a hexadecimal number, to make the distinction even clearer. For example, (2) becomes

in hexadecimalese. Uppercase digits ABCDEF are often used instead of abcdef, because #9E3779B97F4A7C16 looks better than #9e3779b97f4a7c16 in some contexts; there is no difference in meaning.

```

"Of the 256th squadron?"

"Of the fighting 256th Squadron," Yossarian replied.

... "That's two to the fighting eighth power."

— JOSEPH HELLER, Catch-22 (1961)

```

A 16-bit code that supports nearly every modern language became an international standard during the 1990s. This code, known as Unicode or ISO/IEC 10646 UCS-2, includes not only Greek letters like  $\Sigma$  and  $\sigma$  (#03a3 and #03c3), Cyrillic letters like III and III (#0429 and #0449), Armenian letters like C and (#0547 and #0577), Hebrew letters like V (#05e9), Arabic letters like  $\tilde{V}$  (#0634), and Indian letters like III (#0936) or II (#09b6) or II (#0b36) or II (#0bb7), etc., but also tens of thousands of East Asian ideographs such as the Chinese character for mathematics and computing,  $\tilde{V}$  (#7b97). It even has special codes for Roman numerals: MMIX = #216f216f21602169. Ordinary ASCII or Latin-1 characters are represented by simply giving them a leading byte of zero:  $\hat{V}$  pâté is #007000e2007400e9, à  $\hat{V}$  Unicode.

We will use the convenient term wyde to describe a 16-bit quantity like the wide characters of Unicode, because two-byte quantities are quite important in practice. We also need convenient names for four-byte and eight-byte quantities, which we shall call tetrabytes (or "tetras") and octabytes (or "octas"). Thus

```

2 bytes = 1 wyde;

2 wydes = 1 tetra;

2 tetras = 1 octa.

```

One octabyte equals four wydes equals eight bytes equals sixty-four bits.

Bytes and multibyte quantities can, of course, represent numbers as well as alphabetic characters. Using the binary number system,

```

an unsigned byte can express the numbers 0...255; an unsigned wyde can express the numbers 0...65,535; an unsigned tetra can express the numbers 0...4,294,967,295; an unsigned octa can express the numbers 0...18,446,744,073,709,551,615.

```

Integers are also commonly represented by using two's complement notation, in which the leftmost bit indicates the sign: If the leading bit is 1, we subtract  $2^n$  to get the integer corresponding to an n-bit number in this notation. For example, -1 is the signed byte ff; it is also the signed wyde ff, the signed tetrabyte ff, and the signed octabyte ff. In this way

```

a signed byte can express the numbers -128\dots 127; a signed wyde can express the numbers -32,768\dots 32,767; a signed tetra can express the numbers -2,147,483,648\dots 2,147,483,647; a signed octa can express the numbers -9,223,372,036,854,775,808\dots 9,223,372,036,854,775,807.

```

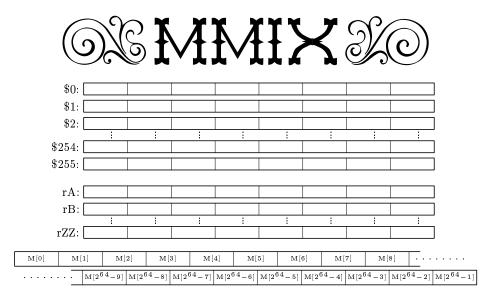

Memory and registers. From a programmer's standpoint, an MMIX computer has  $2^{64}$  cells of *memory* and  $2^8$  general-purpose *registers*, together with  $2^5$  special registers (see Fig. 13). Data is transferred from the memory to the registers, transformed in the registers, and transferred from the registers to the memory. The cells of memory are called M[0], M[1], ..., M[ $2^{64} - 1$ ]; thus if x is any octabyte, M[x] is a byte of memory. The general-purpose registers are called \$0, \$1, ..., \$255; thus if x is any byte, \$x is an octabyte.

The  $2^{64}$  bytes of memory are grouped into  $2^{63}$  wydes,  $M_2[0] = M_2[1] = M[0]M[1]$ ,  $M_2[2] = M_2[3] = M[2]M[3]$ , ...; each wyde consists of two consecutive bytes  $M[2k]M[2k+1] = M[2k] \times 2^8 + M[2k+1]$ , and is denoted either by  $M_2[2k]$  or by  $M_2[2k+1]$ . Similarly there are  $2^{62}$  tetrabytes

```

M_4[4k] = M_4[4k+1] = \dots = M_4[4k+3] = M[4k]M[4k+1]\dots M[4k+3], and 2^{61} octabytes

```

$$M_8[8k] = M_8[8k+1] = \cdots = M_8[8k+7] = M[8k]M[8k+1] \dots M[8k+7].$$

In general if x is any octabyte, the notations  $M_2[x]$ ,  $M_4[x]$ , and  $M_8[x]$  denote the wyde, the tetra, and the octa that contain byte M[x]; we ignore the least

Fig. 13. The MMIX computer, as seen by a programmer, has 256 general-purpose registers and 32 special-purpose registers, together with  $2^{64}$  bytes of virtual memory. Each register holds 64 bits of data.

significant  $\lg t$  bits of x when referring to  $M_t[x]$ . For completeness, we also write  $M_1[x] = M[x]$ , and we define  $M[x] = M[x \mod 2^{64}]$  when x < 0 or  $x \ge 2^{64}$ .

The 32 special registers of MMIX are called rA, rB, ..., rZ, rBB, rTT, rWW, rXX, rYY, and rZZ. Like their general-purpose cousins, they each hold an octabyte. Their uses will be explained later; for example, we will see that rA controls arithmetic interrupts while rR holds the remainder after division.

**Instructions.** MMIX's memory contains instructions as well as data. An *instruction* or "command" is a tetrabyte whose four bytes are conventionally called OP, X, Y, and Z. OP is the *operation code* (or "opcode," for short); X, Y, and Z specify the *operands*. For example, #20010203 is an instruction with OP = #20, X = #01, Y = #02, and Z = #03, and it means "Set \$1 to the sum of \$2 and \$3." The operand bytes are always regarded as unsigned integers.

Each of the 256 possible opcodes has a symbolic form that is easy to remember. For example, opcode #20 is ADD. We will deal almost exclusively with symbolic opcodes; the numeric equivalents can be found, if needed, in Table 1 below, and also in the endpapers of this book.

The X, Y, and Z bytes also have symbolic representations, consistent with the assembly language that we will discuss in Section 1.3.2. For example, the instruction #20010203 is conventionally written 'ADD \$1,\$2,\$3', and the addition instruction in general is written 'ADD \$X,\$Y,\$Z'. Most instructions have three operands, but some of them have only two, and a few have only one. When there are two operands, the first is X and the second is the two-byte quantity YZ; the symbolic notation then has only one comma. For example, the instruction

6

'INCL \$X,YZ' increases register \$X by the amount YZ. When there is only one operand, it is the unsigned three-byte number XYZ, and the symbolic notation has no comma at all. For example, we will see that 'JMP @+4\*XYZ' tells MMIX to find its next instruction by skipping ahead XYZ tetrabytes; the instruction 'JMP @+1000000' has the hexadecimal form #f003d090, because JMP = #f0 and 250000 = #03d090.

We will describe each MMIX instruction both informally and formally. For example, the informal meaning of 'ADD \$X,\$Y,\$Z' is "Set \$X to the sum of \$Y and \$Z"; the formal definition is 's(\$X)  $\leftarrow$  s(\$Y) + s(\$Z)'. Here s(x) denotes the signed integer corresponding to the bit pattern x, according to the conventions of two's complement notation. An assignment like  $s(x) \leftarrow N$  means that x is to be set to the bit pattern for which s(x) = N. (Such an assignment causes integer overflow if N is too large or too small to fit in x. For example, an ADD will overflow if s(\$Y) + s(\$Z) is less than s(\$Z) = S or greater than s(\$Z) = S. When we're discussing an instruction informally, we will often gloss over the possibility of overflow; the formal definition, however, will make everything precise. In general the assignment  $s(x) \leftarrow S$  sets x to the binary representation of S mod S where S is the number of bits in S, and it signals overflow if S is S in S or S is S in S overflow if S in S in S in S in S in S is S in S in

**Loading and storing.** Although MMIX has 256 different opcodes, we will see that they fall into a few easily learned categories. Let's start with the instructions that transfer information between the registers and the memory.

Each of the following instructions has a memory address A obtained by adding \$Y to \$Z. Formally,

$$A = (u(\$Y) + u(\$Z)) \bmod 2^{64}$$

(5)

is the sum of the *unsigned integers* represented by \$Y and \$Z, reduced to a 64-bit number by ignoring any carry that occurs at the left when those two integers are added. In this formula the notation  $\mathbf{u}(x)$  is analogous to  $\mathbf{s}(x)$ , but it considers x to be an unsigned binary number.

- LDB \$X,\$Y,\$Z (load byte):  $s(\$X) \leftarrow s(M_1[A])$ .

- LDW \$X,\$Y,\$Z (load wyde):  $s(X) \leftarrow s(M_2[A])$ .

- LDT \$X,\$Y,\$Z (load tetra):  $s(\$X) \leftarrow s(M_4[A])$ .

- LDO \$X,\$Y,\$Z (load octa):  $s(\$X) \leftarrow s(M_8[A])$ .

These instructions bring data from memory into register \$X, changing the data if necessary from a signed byte, wyde, or tetrabyte to a signed octabyte of the same value. For example, suppose the octabyte  $M_8[1002] = M_8[1000]$  is

$$M[1000]M[1001]...M[1007] = #0123456789abcdef.$$

(6)

Then if \$2 = 1000 and \$3 = 2, we have A = 1002, and

```

LDB $1,$2,$3 sets $1 \leftarrow \#00000000000000045;

```

LDW \$1,\$2,\$3 sets  $$1 \leftarrow \text{\#}0000000000004567};$

LDT \$1,\$2,\$3 sets  $$1 \leftarrow \text{\#}0000000001234567};$

LDO \$1.\$2.\$3 sets  $\$1 \leftarrow \#0123456789$ abcdef.

But if \$3 = 5, so that A = 1005,

```

LDB $1,$2,$3 sets $1 \leftarrow #ffffffffffffffab;

LDW $1,$2,$3 sets $1 \leftarrow #fffffffffffff89ab;

LDT $1,$2,$3 sets $1 \leftarrow #fffffffff89abcdef;

LDO $1,$2,$3 sets $1 \leftarrow #0123456789abcdef.

```

When a signed byte or wyde or tetra is converted to a signed octa, its sign bit is "extended" into all positions to the left.

- LDBU \$X,\$Y,\$Z (load byte unsigned):  $u(\$X) \leftarrow u(M_1[A])$ .

- LDWU \$X,\$Y,\$Z (load wyde unsigned):  $u(X) \leftarrow u(M_2[A])$ .

- LDTU \$X,\$Y,\$Z (load tetra unsigned):  $u(\$X) \leftarrow u(M_4[A])$ .

- LDOU \$X,\$Y,\$Z (load octa unsigned):  $u(\$X) \leftarrow u(M_8[A])$ .

These instructions are analogous to LDB, LDW, LDT, and LDO, but they treat the memory data as unsigned; bit positions at the left of the register are set to zero when a short quantity is being lengthened. Thus, in the example above, LDBU \$1,\$2,\$3 with \$2 + \$3 = 1005 would set \$1  $\leftarrow$  #0000000000000000.

The instructions LDO and LDOU actually have exactly the same behavior, because no sign extension or padding with zeros is necessary when an octabyte is loaded into a register. But a good programmer will use LDO when the sign is relevant and LDOU when it is not; then readers of the program can better understand the significance of what is being loaded.

• LDHT \$X,\$Y,\$Z (load high tetra):  $u(\$X) \leftarrow u(M_4[A]) \times 2^{32}$ .

Here the tetrabyte  $M_4[A]$  is loaded into the *left* half of \$X, and the right half is set to zero. For example, LDHT \$1,\$2,\$3 sets \$1  $\leftarrow$  #89abcdef000000000, assuming (6) with \$2 + \$3 = 1005.

• LDA \$X,\$Y,\$Z (load address):  $u(\$X) \leftarrow A$ .

This instruction, which puts a memory address into a register, is essentially the same as the ADDU instruction described below. Sometimes the words "load address" describe its purpose better than the words "add unsigned."

- STB \$X,\$Y,\$Z (store byte):  $s(M_1[A]) \leftarrow s($X)$ .

- STW \$X,\$Y,\$Z (store wyde):  $s(M_2[A]) \leftarrow s(\$X)$ .

- STT \$X,\$Y,\$Z (store tetra):  $s(M_4[A]) \leftarrow s(X)$ .

- STO \$X,\$Y,\$Z (store octa):  $s(M_8[A]) \leftarrow s($X)$ .

These instructions go the other way, placing register data into the memory. Overflow is possible if the (signed) number in the register lies outside the range of the memory field. For example, suppose register \$1 contains the number -65536 = #ffffffffffff0000. Then if \$2 = 1000, \$3 = 2, and (6) holds,

```

STB $1,$2,$3 sets M_8[1000] \leftarrow \text{\#}0123\,0067\,89ab\,cdef} (with overflow); STW $1,$2,$3 sets M_8[1000] \leftarrow \text{\#}0123\,0000\,89ab\,cdef} (with overflow); STT $1,$2,$3 sets M_8[1000] \leftarrow \text{\#}ffff\,0000\,89ab\,cdef}; STO $1,$2,$3 sets M_8[1000] \leftarrow \text{\#}fffffffffffff0000}.

```

8

- STBU \$X,\$Y,\$Z (store byte unsigned):  $u(M_1[A]) \leftarrow u(\$X) \mod 2^8$ .

- STWU \$X,\$Y,\$Z (store wyde unsigned):  $u(M_2[A]) \leftarrow u(\$X) \bmod 2^{16}$ .

- STTU \$X,\$Y,\$Z (store tetra unsigned):  $u\big(M_4[A]\big) \leftarrow u(\$X) \bmod 2^{32}.$

- STOU \$X,\$Y,\$Z (store octa unsigned):  $u(M_8[A]) \leftarrow u(\$X)$ .

These instructions have exactly the same effect on memory as their signed counterparts STB, STW, STT, and STO, but overflow never occurs.

- STHT \$X,\$Y,\$Z (store high tetra):  $u(M_4[A]) \leftarrow \lfloor u(\$X)/2^{32} \rfloor$ . The left half of register \$X is stored in memory tetrabyte  $M_4[A]$ .

- STCO X,\$Y,\$Z (store constant octabyte):  $u(M_8[A]) \leftarrow X$ . A constant between 0 and 255 is stored in memory octabyte  $M_8[A]$ .

**Arithmetic operators.** Most of MMIX's operations take place strictly between registers. We might as well begin our study of the register-to-register operations by considering addition, subtraction, multiplication, and division, because computers are supposed to be able to compute.

- ADD \$X,\$Y,\$Z (add):  $s(\$X) \leftarrow s(\$Y) + s(\$Z)$ .

- SUB \$X,\$Y,\$Z (subtract):  $s(\$X) \leftarrow s(\$Y) s(\$Z)$ .

- MUL \$X,\$Y,\$Z (multiply):  $s(\$X) \leftarrow s(\$Y) \times s(\$Z)$ .

- DIV \$X,\$Y,\$Z (divide):  $s(\$X) \leftarrow \lfloor s(\$Y)/s(\$Z) \rfloor$  [\$Z \neq 0], and  $s(rR) \leftarrow s(\$Y) \mod s(\$Z)$ .

Sums, differences, and products need no further discussion. The DIV command forms the quotient and remainder as defined in Section 1.2.4; the remainder goes into the special remainder register rR, where it can be examined by using the instruction GET X, rR described below. If the divisor Z is zero, DIV sets  $X \leftarrow 0$  and rR  $\leftarrow Y$  (see Eq. 1.2.4–(1)); an "integer divide check" also occurs.

- ADDU \$X,\$Y,\$Z (add unsigned):  $u(\$X) \leftarrow (u(\$Y) + u(\$Z)) \mod 2^{64}$ .

- SUBU \$X,\$Y,\$Z (subtract unsigned):  $u(\$X) \leftarrow (u(\$Y) u(\$Z)) \mod 2^{64}$ .

- MULU \$X,\$Y,\$Z (multiply unsigned):  $u(rH \$X) \leftarrow u(\$Y) \times u(\$Z)$ .

- DIVU \$X,\$Y,\$Z (divide unsigned):  $u(\$X) \leftarrow \lfloor u(rD \$Y)/u(\$Z) \rfloor$ ,  $u(rR) \leftarrow u(rD \$Y) \mod u(\$Z)$ , if u(\$Z) > u(rD); otherwise  $\$X \leftarrow rD$ ,  $rR \leftarrow \$Y$ .

Arithmetic on unsigned numbers never causes overflow. A full 16-byte product is formed by the MULU command, and the upper half goes into the special *himult register* rH. For example, when the unsigned number #9e3779b97f4a7c16 in (2) and (4) above is multiplied by itself we get

$$rH \leftarrow \text{\#61c8864680b583ea}, \quad \$X \leftarrow \text{\#1bb32095ccdd51e4}.$$

(7)

In this case the value of rH has turned out to be exactly  $2^{64}$  minus the original number #9e3779b97f4a7c16; this is not a coincidence! The reason is that (2) actually gives the first 64 bits of the binary representation of the golden ratio  $\phi^{-1} = \phi - 1$ , if we place a binary radix point at the *left*. (See Table 2 in Appendix A.) Squaring gives us an approximation to the binary representation of  $\phi^{-2} = 1 - \phi^{-1}$ , with the radix point now at the left of rH.

Division with DIVU yields the 8-byte quotient and remainder of a 16-byte dividend with respect to an 8-byte divisor. The upper half of the dividend appears in the special dividend register rD, which is zero at the beginning of a program; this register can be set to any desired value with the command PUT rD, Z described below. If rD is greater than or equal to the divisor, DIVU X,Y,Z simply sets  $X \leftarrow Z$  and  $Z \leftarrow Y$ . (This case always arises when Z is zero.) But DIVU never causes an integer divide check.

The ADDU instruction computes a memory address A, according to definition (5); therefore, as discussed earlier, we sometimes give ADDU the alternative name LDA. The following related commands also help with address calculation.

```

• 2ADDU $X,$Y,$Z (times 2 and add unsigned): u(\$X) \leftarrow (u(\$Y) \times 2 + u(\$Z)) \mod 2^{64}.

```

- 4ADDU \$X,\$Y,\$Z (times 4 and add unsigned):  $u(\$X) \leftarrow (u(\$Y) \times 4 + u(\$Z)) \mod 2^{64}$ .

- 8ADDU \$X,\$Y,\$Z (times 8 and add unsigned):  $u(\$X) \leftarrow (u(\$Y) \times 8 + u(\$Z)) \mod 2^{64}$ .

- 16ADDU \$X,\$Y,\$Z (times 16 and add unsigned):  $u(\$X) \leftarrow (u(\$Y) \times 16 + u(\$Z)) \mod 2^{64}$ .

It is faster to execute the command 2ADDU \$X,\$Y,\$Y than to multiply by 3, if overflow is not an issue.

- NEG \$X,Y,\$Z (negate):  $s(\$X) \leftarrow Y s(\$Z)$ .

- NEGU \$X,Y,\$Z (negate unsigned):  $u(\$X) \leftarrow (Y u(\$Z)) \mod 2^{64}$ .

In these commands Y is simply an unsigned constant, not a register number (just as X was an unsigned constant in the STCO instruction). Usually Y is zero, in which case we can write simply NEG \$X,\$Z or NEGU \$X,\$Z.

- SL \$X,\$Y,\$Z (shift left):  $s(\$X) \leftarrow s(\$Y) \times 2^{u(\$Z)}$ .

- SLU \$X,\$Y,\$Z (shift left unsigned):  $u(\$X) \leftarrow (u(\$Y) \times 2^{u(\$Z)}) \mod 2^{64}$ .

- SR \$X,\$Y,\$Z (shift right):  $s(\$X) \leftarrow |s(\$Y)/2^{u(\$Z)}|$ .

- SRU \$X,\$Y,\$Z (shift right unsigned):  $u(\$X) \leftarrow |u(\$Y)/2^{u(\$Z)}|$ .

SL and SLU both produce the same result in \$X, but SL might overflow while SLU never does. SR extends the sign when shifting right, but SRU shifts zeros in from the left. Therefore SR and SRU produce the same result in \$X if and only if \$Y is nonnegative or \$Z is zero. The SL and SR instructions are much faster than MUL and DIV by powers of 2. An SLU instruction is much faster than MULU by a power of 2, although it does not affect rH as MULU does. An SRU instruction is much faster than DIVU by a power of 2, although it is not affected by rD. The notation  $y \ll z$  is often used to denote the result of shifting a binary value y to the left by z bits; similarly,  $y \gg z$  denotes shifting to the right.

```

• CMP $X,$Y,$Z (compare): s(\$X) \leftarrow \big[ s(\$Y) > s(\$Z) \big] - \big[ s(\$Y) < s(\$Z) \big].

• CMPU $X,$Y,$Z (compare unsigned):

```

$s(\$X) \leftarrow [u(\$Y) > u(\$Z)] - [u(\$Y) < u(\$Z)].$

These instructions each set X to either -1, 0, or 1, depending on whether register Y is less than, equal to, or greater than register Z.

Conditional instructions. Several instructions base their actions on whether a register is positive, or negative, or zero, etc.

- CSN \$X,\$Y,\$Z (conditional set if negative): if s(\$Y) < 0, set  $\$X \leftarrow \$Z$ .

- CSZ \$X,\$Y,\$Z (conditional set if zero): if Y = 0, set  $X \leftarrow Z$ .

- CSP \$X,\$Y,\$Z (conditional set if positive): if s(\$Y) > 0, set  $\$X \leftarrow \$Z$ .

- CSOD \$X,\$Y,\$Z (conditional set if odd): if  $s(\$Y) \mod 2 = 1$ , set  $\$X \leftarrow \$Z$ .

- CSNN \$X,\$Y,\$Z (conditional set if nonnegative): if  $s(\$Y) \ge 0$ , set  $\$X \leftarrow \$Z$ .

- CSNZ \$X,\$Y,\$Z (conditional set if nonzero): if  $Y \neq 0$ , set  $X \leftarrow Z$ .

- CSNP \$X,\$Y,\$Z (conditional set if nonpositive): if  $s(\$Y) \le 0$ , set  $\$X \leftarrow \$Z$ .

- CSEV \$X,\$Y,\$Z (conditional set if even): if  $s(\$Y) \mod 2 = 0$ , set  $\$X \leftarrow \$Z$ .

If register \$Y satisfies the stated condition, register \$Z is copied to register \$X; otherwise nothing happens. A register is negative if and only if its leading (leftmost) bit is 1. A register is odd if and only if its trailing (rightmost) bit is 1.

- ZSN \$X,\$Y,\$Z (zero or set if negative):  $X \leftarrow Z[s(Y) < 0]$ .

- ZSZ \$X,\$Y,\$Z (zero or set if zero):  $X \leftarrow Z[Y = 0]$ .

- ZSP \$X,\$Y,\$Z (zero or set if positive):  $X \leftarrow Z[s(Y) > 0]$ .

- ZSOD \$X,\$Y,\$Z (zero or set if odd):  $X \leftarrow Z[s(Y) \mod 2 = 1]$ .

- ZSNN \$X,\$Y,\$Z (zero or set if nonnegative):  $X \leftarrow Z[s(Y) \ge 0]$ .

- ZSNZ \$X,\$Y,\$Z (zero or set if nonzero):  $X \leftarrow Z[Y \neq 0]$ .

- ZSNP \$X,\$Y,\$Z (zero or set if nonpositive):  $X \leftarrow Z[s(Y) \le 0]$ .

- ZSEV \$X,\$Y,\$Z (zero or set if even):  $X \leftarrow Z[s(Y) \mod 2 = 0]$ .

If register \$Y satisfies the stated condition, register \$Z is copied to register \$X; otherwise register \$X is set to zero.

**Bitwise operations.** We often find it useful to think of an octabyte x as a  $vector \mathbf{v}(x)$  of 64 individual bits, and to perform operations simultaneously on each component of two such vectors.

- AND \$X,\$Y,\$Z (bitwise and):  $v(\$X) \leftarrow v(\$Y) \wedge v(\$Z)$ .

- OR \$X,\$Y,\$Z (bitwise or):  $v(\$X) \leftarrow v(\$Y) \lor v(\$Z)$ .

- XOR \$X,\$Y,\$Z (bitwise exclusive-or):  $v(\$X) \leftarrow v(\$Y) \oplus v(\$Z)$ .

- ANDN \$X,\$Y,\$Z (bitwise and-not):  $v(\$X) \leftarrow v(\$Y) \land \bar{v}(\$Z)$ .

- ORN \$X,\$Y,\$Z (bitwise or-not):  $v(\$X) \leftarrow v(\$Y) \vee \bar{v}(\$Z)$ .

- NAND \$X,\$Y,\$Z (bitwise not-and):  $\bar{\mathbf{v}}(\$\mathbf{X}) \leftarrow \mathbf{v}(\$\mathbf{Y}) \wedge \mathbf{v}(\$\mathbf{Z})$ .

- NOR \$X,\$Y,\$Z (bitwise not-or):  $\bar{\mathbf{v}}(\$\mathbf{X}) \leftarrow \mathbf{v}(\$\mathbf{Y}) \vee \mathbf{v}(\$\mathbf{Z})$ .

- NXOR \$X,\$Y,\$Z (bitwise not-exclusive-or):  $\bar{v}(\$X) \leftarrow v(\$Y) \oplus v(\$Z)$ .

Here  $\bar{\mathbf{v}}$  denotes the *complement* of vector  $\mathbf{v}$ , obtained by changing 0 to 1 and 1 to 0. The binary operations  $\wedge$ ,  $\vee$ , and  $\oplus$ , defined by the rules

$$0 \land 0 = 0, & 0 \lor 0 = 0, & 0 \oplus 0 = 0, \\

0 \land 1 = 0, & 0 \lor 1 = 1, & 0 \oplus 1 = 1, \\

1 \land 0 = 0, & 1 \lor 0 = 1, & 1 \oplus 0 = 1, \\

1 \land 1 = 1, & 1 \lor 1 = 1, & 1 \oplus 1 = 0,

\end{cases} (8)$$

are applied independently to each bit. Anding is the same as multiplying or taking the minimum; oring is the same as taking the maximum. Exclusive-oring is the same as adding mod 2.

- MUX \$X,\$Y,\$Z (bitwise multiplex):  $v(\$X) \leftarrow (v(\$Y) \land v(rM)) \lor (v(\$Z) \land \overline{v}(rM))$ . The MUX operation combines two bit vectors by looking at the special multiplex mask register rM, choosing bits of \$Y where rM is 1 and bits of \$Z where rM is 0.

- SADD \$X,\$Y,\$Z (sideways add):  $s(\$X) \leftarrow s(\sum (v(\$Y) \land \bar{v}(\$Z)))$ . The SADD operation counts the number of bit positions in which register \$Y has a 1 while register \$Z has a 0.

Bytewise operations. Similarly, we can regard an octabyte x as a vector b(x)of eight individual bytes, each of which is an integer between 0 and 255; or we can think of it as a vector  $\mathbf{w}(x)$  of four individual wydes, or a vector  $\mathbf{t}(x)$  of two unsigned tetras. The following operations deal with all components at once.

- BDIF \$X,\$Y,\$Z (byte difference):  $b(\$X) \leftarrow b(\$Y) = b(\$Z)$ .

- WDIF \$X,\$Y,\$Z (wyde difference):  $w(\$X) \leftarrow w(\$Y) w(\$Z)$

- TDIF \$X,\$Y,\$Z (tetra difference):  $t(\$X) \leftarrow t(\$Y) t(\$Z)$ .

- ODIF \$X,\$Y,\$Z (octa difference):  $u(\$X) \leftarrow u(\$Y) u(\$Z)$ .

Here - denotes the operation of saturating subtraction,

$$y - z = \max(0, y - z). \tag{9}$$

These operations have important applications to text processing, as well as to computer graphics (when the bytes or wydes represent pixel values). Exercises 27–30 discuss some of their basic properties.

We can also regard an octabyte as an  $8 \times 8$  Boolean matrix, that is, as an  $8 \times 8$  array of 0s and 1s. Let m(x) be the matrix whose rows from top to bottom are the bytes of x from left to right; and let  $m^{T}(x)$  be the transposed matrix, whose *columns* are the bytes of x. For example, if  $x = {}^{\#}9e3779b97f4a7c16$  is the octabyte (2), we have

$$\mathbf{m}(x) = \begin{pmatrix} 1 & 0 & 0 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 & 0 & 1 & 1 & 1 \\ 0 & 1 & 1 & 1 & 1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 1 & 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 1 & 0 & 1 & 1 \end{pmatrix}, \qquad \mathbf{m}^{\mathsf{T}}(x) = \begin{pmatrix} 1 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 1 & 1 & 1 & 0 \\ 0 & 1 & 1 & 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 1 & 1 & 1 & 0 & 0 \end{pmatrix}. \tag{10}$$

This interpretation of octabytes suggests two operations that are quite familiar to mathematicians, but we will pause a moment to define them from scratch.

If A is an  $m \times n$  matrix and B is an  $n \times s$  matrix, and if  $\circ$  and  $\bullet$  are binary operations, the generalized matrix product  $A \circ B$  is the  $m \times s$  matrix C defined by

$$C_{ij} = (A_{i1} \bullet B_{1j}) \circ (A_{i2} \bullet B_{2j}) \circ \cdots \circ (A_{in} \bullet B_{nj}) \tag{11}$$

for  $1 \le i \le m$  and  $1 \le j \le s$ . [See K. E. Iverson, A Programming Language (Wiley, 1962), 23–24; we assume that o is associative. An ordinary matrix product is obtained when  $\circ$  is + and  $\bullet$  is  $\times$ , but we obtain important operations

on Boolean matrices if we let  $\circ$  be  $\vee$  or  $\oplus$ :

$$(A_{\times}^{\vee} B)_{ij} = A_{i1}B_{1j} \vee A_{i2}B_{2j} \vee \dots \vee A_{in}B_{nj};$$

(12)

$$(A \times^{\oplus} B)_{ij} = A_{i1}B_{1j} \oplus A_{i2}B_{2j} \oplus \cdots \oplus A_{in}B_{nj}. \tag{13}$$

Notice that if the rows of A each contain at most one 1, at most one term in (12) or (13) is nonzero. The same is true if the columns of B each contain at most one 1. Therefore  $A_{\times}^{\vee}B$  and  $A_{\times}^{\oplus}B$  both turn out to be the same as the ordinary matrix product  $A_{\times}^{+}B = AB$  in such cases.

- MOR \$X,\$Y,\$Z (multiple or):  $m^T(\$X) \leftarrow m^T(\$Y) \begin{subarray}{c} \downarrow \\ m^T(\$Z) \end{subarray} \\ m^T(\$Z) \end{subarray} \\ equivalently, m(\$X) \leftarrow m(\$Z) \begin{subarray}{c} \downarrow \\ m(\$Y) \end{subarray} \\ (See exercise 32.) \\ m^T(\$X) \end{subarray} \\ m$

- MXOR \$X,\$Y,\$Z (multiple exclusive-or):  $m^T(\$X) \leftarrow m^T(\$Y) \overset{\oplus}{\times} m^T(\$Z)$ ; equivalently,  $m(\$X) \leftarrow m(\$Z) \overset{\oplus}{\times} m(\$Y)$ .

These operations essentially set each byte of \$X by looking at the corresponding byte of \$Z and using its bits to select bytes of \$Y; the selected bytes are then ored or xored together. If, for example, we have

$$Z = 0102040810204080,$$

(14)

then both MOR and MXOR will set register \$X to the byte reversal of register \$Y: The kth byte from the left of \$X will be set to the kth byte from the right of \$Y, for  $1 \le k \le 8$ . On the other hand if \$Z = #00000000000000ff, MOR and MXOR will set all bytes of \$X to zero except for the rightmost byte, which will become either the OR or the XOR of all eight bytes of \$Y. Exercises 33-37 illustrate some of the many practical applications of these versatile commands.

Floating point operators. MMIX includes a full implementation of the famous IEEE/ANSI Standard 754 for floating point arithmetic. Complete details of the floating point operations appear in Section 4.2 and in the MMIXware document; a rough summary will suffice for our purposes here.

Every octabyte x represents a floating binary number f(x) determined as follows: The leftmost bit of x is the sign (0 = +, 1 = -); the next 11 bits are the *exponent* E; the remaining 52 bits are the *fraction* F. The value represented is then

```

\begin{array}{c} \pm 0.0, \ {\rm if} \ E=F=0 \ ({\rm zero}); \\ \pm 2^{-1074} {\rm F}, \ {\rm if} \ E=0 \ {\rm and} \ {\rm F} \neq 0 \ ({\rm denormal}); \\ \pm 2^{{\rm E}-1023} (1+{\rm F}/2^{52}), \ {\rm if} \ 0<{\rm E} < 2047 \ ({\rm normal}); \\ \pm \infty, \ {\rm if} \ E=2047 \ {\rm and} \ {\rm F}=0 \ ({\rm infinite}); \\ \pm {\rm NaN}({\rm F}/2^{52}), \ {\rm if} \ E=2047 \ {\rm and} \ {\rm F} \neq 0 \ ({\rm Not-a-Number}). \end{array}

```

The "short" floating point number f(t) represented by a tetrabyte t is similar, but its exponent part has only 8 bits and its fraction has only 23; the normal case 0 < E < 255 of a short float represents  $\pm 2^{E-127}(1 + F/2^{23})$ .

- FADD \$X,\$Y,\$Z (floating add):  $f(\$X) \leftarrow f(\$Y) + f(\$Z)$ .

- FSUB \$X,\$Y,\$Z (floating subtract):  $f(\$X) \leftarrow f(\$Y) f(\$Z)$ .

- FMUL \$X,\$Y,\$Z (floating multiply):  $f(\$X) \leftarrow f(\$Y) \times f(\$Z)$ .

- FDIV \$X,\$Y,\$Z (floating divide):  $f(\$X) \leftarrow f(\$Y)/f(\$Z)$ .

- FREM \$X,\$Y,\$Z (floating remainder):  $f(\$X) \leftarrow f(\$Y)$  rem f(\$Z).

- FSQRT \$X,\$Z or FSQRT \$X,Y,\$Z (floating square root):  $f(\$X) \leftarrow f(\$Z)^{1/2}$ .

- FINT \$X,\$Z or FINT \$X,Y,\$Z (floating integer):  $f(\$X) \leftarrow \inf f(\$Z)$ .

- FCMP \$X,\$Y,\$Z (floating compare):  $s(\$X) \leftarrow [f(\$Y) > f(\$Z)] [f(\$Y) < f(\$Z)]$ .

- FEQL \$X,\$Y,\$Z (floating equal to):  $s(\$X) \leftarrow [f(\$Y) = f(\$Z)]$ .

- FUN \$X,\$Y,\$Z (floating unordered):  $s(\$X) \leftarrow [f(\$Y) \parallel f(\$Z)]$ .

- FCMPE \$X,\$Y,\$Z (floating compare with respect to epsilon):  $s(\$X) \leftarrow \lceil f(\$Y) \succ f(\$Z) \ (f(rE)) \rceil \lceil f(\$Y) \prec f(\$Z) \ (f(rE)) \rceil$ , see 4.2.2–(21).

- FEQLE \$X,\$Y,\$Z (floating equivalent with respect to epsilon):  $s(\$X) \leftarrow [f(\$Y) \approx f(\$Z) (f(rE))], \text{ see } 4.2.2-(24).$

- FUNE \$X,\$Y,\$Z (floating unordered with respect to epsilon):  $s(\$X) \leftarrow [f(\$Y) \parallel f(\$Z) (f(rE))].$

- FIX \$X,\$Z or FIX \$X,Y,\$Z (convert floating to fixed):  $s(\$X) \leftarrow int f(\$Z)$ .

- FIXU \$X,\$Z or FIXU \$X,Y,\$Z (convert floating to fixed unsigned):  $u(\$X) \leftarrow (\inf f(\$Z)) \mod 2^{64}$ .

- FLOT \$X,\$Z or FLOT \$X,Y,\$Z (convert fixed to floating):  $f(\$X) \leftarrow s(\$Z)$ .

- FLOTU \$X,\$Z or FLOTU \$X,Y,\$Z (convert fixed to floating unsigned):  $f($X) \leftarrow u($Z)$ .

- SFLOT \$X,\$Z or SFLOT \$X,Y,\$Z (convert fixed to short float):  $f(\$X) \leftarrow f(T) \leftarrow s(\$Z)$ .

- SFLOTU \$X,\$Z or SFLOTU \$X,Y,\$Z (convert fixed to short float unsigned):  $f(\$X) \leftarrow f(T) \leftarrow u(\$Z)$ .

- LDSF \$X,\$Y,\$Z or LDSF \$X,A (load short float):  $f(X) \leftarrow f(M_4[A])$ .

- STSF \$X,\$Y,\$Z or STSF \$X,A (store short float):  $f(M_4[A]) \leftarrow f(\$X)$ .

Assignment to a floating point quantity uses the current rounding mode to determine the appropriate value when an exact value cannot be assigned. Four rounding modes are supported: 1 (ROUND\_OFF), 2 (ROUND\_UP), 3 (ROUND\_DOWN), and 4 (ROUND\_NEAR). The Y field of FSQRT, FINT, FIX, FIXU, FLOT, FLOTU, SFLOT, and SFLOTU can be used to specify a rounding mode other than the current one, if desired. For example, FIX \$X,ROUND\_UP,\$Z sets  $s(\$X) \leftarrow \lceil f(\$Z) \rceil$ . Operations SFLOT and SFLOTU first round as if storing into an anonymous tetrabyte T, then they convert that number to octabyte form.

The 'int' operation rounds to an integer. The operation  $y \operatorname{rem} z$  is defined to be y-nz, where n is the nearest integer to y/z, or the nearest even integer in case of a tie. Special rules apply when the operands are infinite or NaN, and special conventions govern the sign of a zero result. The values +0.0 and -0.0 have different floating point representations, but FEQL calls them equal. All such technicalities are explained in the MMIXware document, and Section 4.2 explains why the technicalities are important.

Immediate constants. Programs often need to deal with small constant numbers. For example, we might want to add or subtract 1 from a register, or we might want to shift by 32, etc. In such cases it's a nuisance to load the small constant from memory into another register. So MMIX provides a general mechanism by which such constants can be obtained "immediately" from an

instruction itself: Every instruction we have discussed so far has a variant in which \$Z is replaced by the number Z, unless the instruction treats \$Z as a floating point number.

For example, 'ADD \$X,\$Y,\$Z' has a counterpart 'ADD \$X,\$Y,Z', meaning  $s(\$X) \leftarrow s(\$Y) + Z;$  'SRU \$X,\$Y,\$Z' has a counterpart 'SRU \$X,\$Y,Z', meaning  $u(\$X) \leftarrow \left\lfloor u(\$Y)/2^Z \right\rfloor;$  'FLOT \$X,\$Z' has a counterpart 'FLOT \$X,Z', meaning  $f(\$X) \leftarrow Z.$  But 'FADD \$X,\$Y,\$Z' has no immediate counterpart.

The opcode for 'ADD \$X,\$Y,\$Z' is #20 and the opcode for 'ADD \$X,\$Y,Z' is #21; we use the same symbol ADD in both cases for simplicity. In general the opcode for the immediate variant of an operation is one greater than the opcode for the register variant.

Several instructions also feature wyde immediate constants, which range from #0000 = 0 to #ffff = 65535. These constants, which appear in the YZ bytes, can be shifted into the high, medium high, medium low, or low wyde positions of an octabyte.

- SETH \$X,YZ (set high wyde):  $u(\$X) \leftarrow YZ \times 2^{48}$ .

- SETMH \$X,YZ (set medium high wyde):  $u(\$X) \leftarrow YZ \times 2^{32}$ .

- SETML \$X, YZ (set medium low wyde):  $u(\$X) \leftarrow YZ \times 2^{16}$ .

- SETL \$X,YZ (set low wyde):  $u(\$X) \leftarrow YZ$ .

- INCH \$X,YZ (increase by high wyde):  $u(\$X) \leftarrow (u(\$X) + YZ \times 2^{48}) \mod 2^{64}$ .

- INCMH \$X,YZ (increase by medium high wyde):  $u(\$X) \leftarrow (u(\$X) + YZ \times 2^{32}) \mod 2^{64}$ .

- INCML \$X,YZ (increase by medium low wyde):  $u(\$X) \leftarrow (u(\$X) + YZ \times 2^{16}) \mod 2^{64}$ .

- INCL \$X,YZ (increase by low wyde):  $u(\$X) \leftarrow (u(\$X) + YZ) \mod 2^{64}$ .

- ORH \$X,YZ (bitwise or with high wyde):  $v(\$X) \leftarrow v(\$X) \lor v(YZ \ll 48)$ .

- ORMH \$X,YZ (bitwise or with medium high wyde):  $v(\$X) \leftarrow v(\$X) \lor v(YZ \ll 32)$ .

- ORML \$X,YZ (bitwise or with medium low wyde):  $v(\$X) \leftarrow v(\$X) \lor v(YZ \ll 16)$ .

- ORL \$X,YZ (bitwise or with low wyde):  $v(\$X) \leftarrow v(\$X) \lor v(YZ)$ .

- ANDNH \$X,YZ (bitwise and-not high wyde):  $v(\$X) \leftarrow v(\$X) \land \bar{v}(YZ \ll 48)$ .

- ANDNMH \$X,YZ (bitwise and-not medium high wyde):  $v(\$X) \leftarrow v(\$X) \wedge \bar{v}(YZ \ll 32)$ .

- ANDNML \$X,YZ (bitwise and-not medium low wyde):  $v(\$X) \leftarrow v(\$X) \land \bar{v}(YZ \ll 16)$ .

- ANDNL \$X, YZ (bitwise and-not low wyde):  $v(\$X) \leftarrow v(\$X) \land \bar{v}(YZ)$ .

Using at most four of these instructions, we can get any desired octabyte into a register without loading anything from the memory. For example, the commands

```

SETH $0,#0123; INCMH $0,#4567; INCML $0,#89ab; INCL $0,#cdef put #0123456789abcdef into register $0.

```

The MMIX assembly language allows us to write SET as an abbreviation for SETL, and SET \$X,\$Y as an abbreviation for the common operation OR \$X,\$Y,0.

**Jumps and branches.** Instructions are normally executed in their natural sequence. In other words, the command that is performed after MMIX has obeyed the tetrabyte in memory location @ is normally the tetrabyte found in memory location @+4. (The symbol @ denotes the place where we're "at.") But jump and branch instructions allow this sequence to be interrupted.

## • JMP RA (jump): $@ \leftarrow RA$ .

Here RA denotes a three-byte relative address, which could be written more explicitly as @+4\*XYZ, namely XYZ tetrabytes following the current location @. For example, 'JMP @+4\*2' is a symbolic form for the tetrabyte #f0000002; if this instruction appears in location #1000, the next instruction to be executed will be the one in location #1008. We might in fact write 'JMP #1008'; but then the value of XYZ would depend on the location jumped from.

Relative offsets can also be negative, in which case the opcode increases by 1 and XYZ is the offset plus  $2^{24}$ . For example, 'JMP @-4\*2' is the tetrabyte #f1fffffe. Opcode #f0 tells the computer to "jump forward" and opcode #f1 tells it to "jump backward," but we write both as JMP. In fact, we usually write simply 'JMP Addr' when we want to jump to location Addr, and the MMIX assembly program figures out the appropriate opcode and the appropriate value of XYZ. Such a jump will be possible unless we try to stray more than about 67 million bytes from our present location.

• GO \$X,\$Y,\$Z (go):  $u($X) \leftarrow @+4$ , then  $@ \leftarrow A$ .

The GO instruction allows us to jump to an absolute address, anywhere in memory; this address A is calculated by formula (5), exactly as in the load and store commands. Before going to the specified address, the location of the instruction that would ordinarily have come next is placed into register X. Therefore we could return to that location later by saying, for example, 'GO X,X,X,O', with Z=0 as an immediate constant.

- BN \$X,RA (branch if negative): if s(\$X) < 0, set  $@ \leftarrow RA$ .

- BZ \$X,RA (branch if zero): if X = 0, set  $\leftarrow RA$ .

- BP \$X, RA (branch if positive): if s(\$X) > 0, set @  $\leftarrow RA$ .

- BOD \$X, RA (branch if odd): if  $s(\$X) \mod 2 = 1$ , set  $@ \leftarrow RA$ .

- BNN \$X,RA (branch if nonnegative): if  $s(\$X) \ge 0$ , set @  $\leftarrow RA$ .

- BNZ \$X,RA (branch if nonzero): if  $X \neq 0$ , set  $\leftarrow RA$ .

- BNP \$X,RA (branch if nonpositive): if  $s(\$X) \le 0$ , set  $@ \leftarrow RA$ .

- BEV \$X,RA (branch if even): if  $s(\$X) \mod 2 = 0$ , set @  $\leftarrow RA$ .

A branch instruction is a conditional jump that depends on the contents of register X. The range of destination addresses RA is more limited than it was with JMP, because only two bytes are available to express the relative offset; but still we can branch to any tetrabyte between  $0 - 2^{18}$  and  $0 + 2^{18} - 4$ .

- PBN \$X,RA (probable branch if negative): if s(\$X) < 0, set  $@ \leftarrow RA$ .

- PBZ \$X,RA (probable branch if zero): if X = 0, set  $\leftarrow RA$ .

- PBP \$X,RA (probable branch if positive): if s(\$X) > 0, set @  $\leftarrow RA$ .

- PBOD \$X,RA (probable branch if odd): if  $s(\$X) \mod 2 = 1$ , set @  $\leftarrow RA$ .

- PBNN \$X,RA (probable branch if nonnegative): if  $s(\$X) \ge 0$ , set  $@ \leftarrow RA$ .

- PBNZ \$X, RA (probable branch if nonzero): if  $X \neq 0$ , set  $\leftarrow RA$ .

- PBNP \$X,RA (probable branch if nonpositive): if  $s(\$X) \le 0$ , set  $@ \leftarrow RA$ .

- PBEV \$X,RA (probable branch if even): if  $s(\$X) \mod 2 = 0$ , set @  $\leftarrow RA$ .

High-speed computers usually work fastest if they can anticipate when a branch will be taken, because foreknowledge helps them look ahead and get ready for future instructions. Therefore MMIX encourages programmers to give hints about whether branching is likely or not. Whenever a branch is expected to be taken more than half of the time, a wise programmer will say PB instead of B.

- \*Subroutine calls. MMIX also has several instructions that facilitate efficient communication between subprograms, via a register stack. The details are somewhat technical and we will defer them until Section 1.4; an informal description will suffice here. Short programs do not need to use these features.

- PUSHJ \$X,RA (push registers and jump): push(X) and set  $rJ \leftarrow @+4$ , then set  $@\leftarrow RA$ .

- PUSHGO \$X,\$Y,\$Z (push registers and go): push(X) and set  $rJ \leftarrow @+4$ , then set  $@\leftarrow A$ .

The special return-jump register rJ is set to the address of the tetrabyte following the PUSH command. The action "push(X)" means, roughly speaking, that local registers 0 through X are saved and made temporarily inaccessible. What used to be X+1 is now 0, what used to be X+1 is now 1, etc. But all registers f for f remain unchanged; rG is the special global threshold register, whose value always lies between 32 and 255, inclusive.

Register \$k is called *global* if  $k \ge \mathrm{rG}$ . It is called *local* if  $k < \mathrm{rL}$ ; here  $\mathrm{rL}$  is the special *local threshold register*, which tells how many local registers are currently active. Otherwise, namely if  $\mathrm{rL} \le k < \mathrm{rG}$ , register \$k is called *marginal*, and \$k is equal to zero whenever it is used as a source operand in a command. If a marginal register \$k is used as a destination operand in a command,  $\mathrm{rL}$  is automatically increased to k+1 before the command is performed, thereby making \$k local.

- POP X,YZ (pop registers and return): pop(X), then  $@ \leftarrow rJ + 4 * YZ$ . Here "pop(X)" means, roughly speaking, that all but X of the current local registers become marginal, and then the local registers hidden by the most recent "push" that has not yet been "popped" are restored to their former values. Full details appear in Section 1.4′, together with numerous examples.

- SAVE \$X,0 (save process state):  $u(\$X) \leftarrow context$ .

- UNSAVE \$Z (restore process state): context  $\leftarrow$  u(\$Z).

The SAVE instruction stores all current registers in memory at the top of the register stack, and puts the address of the topmost stored octabyte into u(\$X). Register \$X must be global; that is, X must be  $\ge rG$ . All of the currently local and global registers are saved, together with special registers like rA, rD, rE, rG, rH, rJ, rM, rR, and several others that we have not yet discussed. The UNSAVE instruction takes the address of such a topmost octabyte and restores the associated context, essentially undoing a previous SAVE. The value of rL is set to zero by SAVE, but restored by UNSAVE. MMIX has special registers called

the register stack offset (rO) and register stack pointer (rS), which control the PUSH, POP, SAVE, and UNSAVE operations. (Again, full details can be found in Section 1.4'.)

- \*System considerations. Several opcodes, intended primarily for ultrafast and/or parallel versions of the MMIX architecture, are of interest only to advanced users, but we should at least mention them here. Some of the associated operations are similar to the "probable branch" commands, in the sense that they give hints to the machine about how to plan ahead for maximum efficiency. Most programmers do not need to use these instructions, except perhaps SYNCID.

- LDUNC \$X,\$Y,\$Z (load octa uncached):  $s(\$X) \leftarrow s(M_8[A])$ .

- STUNC \$X,\$Y,\$Z (store octa uncached):  $s(M_8[A]) \leftarrow s(\$X)$ .

These commands perform the same operations as LDO and STO, but they also inform the machine that the loaded or stored octabyte and its near neighbors will probably not be read or written in the near future.

• PRELD X, \$Y, \$Z (preload data).

Says that many of the bytes M[A] through M[A+X] will probably be loaded or stored in the near future.

• PREST X, \$Y, \$Z (prestore data).

Says that all of the bytes M[A] through M[A + X] will definitely be written (stored) before they are next read (loaded).

• PREGO X, \$Y, \$Z (prefetch to go).

Says that many of the bytes M[A] through M[A+X] will probably be used as instructions in the near future.

• SYNCID X, \$Y, \$Z (synchronize instructions and data).

Says that all of the bytes M[A] through M[A+X] must be fetched again before being interpreted as instructions. MMIX is allowed to assume that a program's instructions do not change after the program has begun, unless the instructions have been prepared by SYNCID. (See exercise 57.)

• SYNCD X, \$Y, \$Z (synchronize data).

Says that all of bytes M[A] through M[A+X] must be brought up to date in the physical memory, so that other computers and input/output devices can read them.

• SYNC XYZ (synchronize).

Restricts parallel activities so that different processors can cooperate reliably; see MMIXware for details. XYZ must be 0, 1, 2, or 3.

• CSWAP \$X,\$Y,\$Z (compare and swap octabytes).

If  $u(M_8[A]) = u(rP)$ , where rP is the special prediction register, set  $u(M_8[A]) \leftarrow u(\$X)$  and  $u(\$X) \leftarrow 1$ . Otherwise set  $u(rP) \leftarrow u(M_8[A])$  and  $u(\$X) \leftarrow 0$ . This is an atomic (indivisible) operation, useful when independent computers share a common memory.

• LDVTS \$X,\$Y,\$Z (load virtual translation status).

This instruction, described in MMIXware, is for the operating system only.

\*Interrupts. The normal flow of instructions from one tetrabyte to the next can be changed not only by jumps and branches but also by less predictable events like overflow or external signals. Real-world machines must also cope with such things as security violations and hardware failures. MMIX distinguishes two kinds of program interruptions: "trips" and "traps." A trip sends control to a trip handler, which is part of the user's program; a trap sends control to a trap handler, which is part of the operating system.

Eight kinds of exceptional conditions can arise when MMIX is doing arithmetic, namely integer divide check (D), integer overflow (V), float-to-fix overflow (W), invalid floating operation (I), floating overflow (O), floating underflow (U), floating division by zero (Z), and floating inexact (X). The special arithmetic status register rA holds current information about all these exceptions. The eight bits of its rightmost byte are called its event bits, and they are named D\_BIT (#80), V\_BIT (#40), ..., X\_BIT (#01), in order DVWIOUZX.

The eight bits just to the left of the event bits in rA are called the *enable bits*; they appear in the same order DVWIOUZX. When an exceptional condition occurs during some arithmetic operation, MMIX looks at the corresponding enable bit before proceeding to the next instruction. If the enable bit is 0, the corresponding event bit is set to 1; otherwise the machine invokes a trip handler by "tripping" to location #10 for exception D, #20 for exception V, ..., #80 for exception X. Thus the event bits of rA record the exceptions that have not caused trips. (If more than one enabled exception occurs, the leftmost one takes precedence. For example, simultaneous O and X is handled by O.)

The two bits of rA just to the left of the enable bits hold the current rounding mode, mod 4. The other 46 bits of rA should be zero. A program can change the setting of rA at any time, using the PUT command discussed below.

### • TRIP X,Y,Z or TRIP X,YZ or TRIP XYZ (trip).

This command forces a trip to the handler at location #00.

Whenever a trip occurs, MMIX uses five special registers to record the current state: the bootstrap register rB, the where-interrupted register rW, the execution register rX, the Y operand register rY, and the Z operand register rZ. First rB is set to \$255, then \$255 is set to rJ, and rW is set to @ + 4. The left half of rX is set to #80000000, and the right half is set to the instruction that tripped. If the interrupted instruction was not a store command, rY is set to \$Y and rZ is set to \$Z (or to Z in case of an immediate constant); otherwise rY is set to A (the memory address of the store command) and rZ is set to \$X (the quantity to be stored). Finally control passes to the handler by setting @ to the handler address (#00 or #10 or ··· or #80).

#### • TRAP X, Y, Z or TRAP X, YZ or TRAP XYZ (trap).

This command is analogous to TRIP, but it forces a trap to the operating system. Special registers rBB, rWW, rXX, rYY, and rZZ take the place of rB, rW, rX, rY, and rZ; the special trap address register rT supplies the address of the trap handler, which is placed in @. Section 1.3.2' describes several TRAP commands that provide simple input/output operations. The normal way to conclude a

program is to say 'TRAP 0'; this instruction is the tetrabyte #00000000, so you might run into it by mistake.

The MMIXware document gives further details about external interrupts, which are governed by the special interrupt mask register rK and interrupt request register rQ. Dynamic traps, which arise when rK  $\wedge$  rQ  $\neq$  0, are handled at address rTT instead of rT.

• RESUME 0 (resume after interrupt).

If s(rX) is negative, MMIX simply sets  $@ \leftarrow rW$  and takes its next instruction from there. Otherwise, if the leading byte of rX is zero, MMIX sets  $@ \leftarrow rW - 4$  and executes the instruction in the lower half of rX as if it had appeared in that location. (This feature can be used even if no interrupt has occurred. The inserted instruction must not itself be RESUME.) Otherwise MMIX performs special actions described in the MMIXware document and of interest primarily to the operating system; see exercise 1.4.3'-14.

The complete instruction set. Table 1 shows the symbolic names of all 256 opcodes, arranged by their numeric values in hexadecimal notation. For example, ADD appears in the upper half of the row labeled #2x and in the column labeled #0 at the top, so ADD is opcode #20; ORL appears in the lower half of the row labeled #Ex and in the column labeled #B at the bottom, so ORL is opcode #EB.

Table 1 actually says 'ADD[I]', not 'ADD', because the symbol ADD really stands for two opcodes. Opcode #20 arises from ADD \$X,\$Y,\$Z using register \$Z, while opcode #21 arises from ADD \$X,\$Y,Z using the immediate constant Z. When a distinction is necessary, we say that opcode #20 is ADD and opcode #21 is ADDI ("add immediate"); similarly, #FO is JMP and #F1 is JMPB ("jump backward"). This gives every opcode a unique name. However, the extra I and B are generally dropped for convenience when we write MMIX programs.

We have discussed nearly all of MMIX's opcodes. Two of the stragglers are

- GET \$X, Z (get from special register):  $u(\$X) \leftarrow u(g[Z])$ , where  $0 \le Z < 32$ .

- PUT X,\$Z (put into special register):  $u(g[X]) \leftarrow u(\$Z)$ , where  $0 \le X < 32$ .

Each special register has a code number between 0 and 31. We speak of registers rA, rB, ..., as aids to human understanding; but register rA is really g[21] from the machine's point of view, and register rB is really g[0], etc. The code numbers appear in Table 2 on page 21.

GET commands are unrestricted, but certain things cannot be PUT: No value can be put into rG that is greater than 255, less than 32, or less than the current setting of rL. No value can be put into rA that is greater than #3ffff. If a program tries to increase rL with the PUT command, rL will stay unchanged. Moreover, a program cannot PUT anything into rC, rN, rO, rS, rI, rT, rTT, rK, rQ, rU, or rV; these "extraspecial" registers have code numbers in the range 8–18.

Most of the special registers have already been mentioned in connection with specific instructions, but MMIX also has a "clock register" or cycle counter, rC, which keeps advancing; an interval counter, rI, which keeps decreasing, and which requests an interrupt when it reaches zero; a serial number register, rN, which gives each MMIX machine a unique number; a usage counter, rU, which

Table 1

THE OPCODES OF MMIX

|       | # O               | # 1       | #2                         | #3        | #4                                    | # 5       | #6                         | #7       |       |  |

|-------|-------------------|-----------|----------------------------|-----------|---------------------------------------|-----------|----------------------------|----------|-------|--|

| # 0 x | TRAP 5v           | FCMP v    | FUN v                      | FEQL v    | FADD 4v                               | FIX 4v    | FSUB 4v                    | FIXU 4v  | # 0x  |  |

| "OX   | FLOT[I] 4v        |           | FLOTU[I] 4v                |           | SFLOT[I] 4v                           |           | SFLOTU[I] 4v               |          | "UX   |  |

| # 1 x | FMUL 4v           | FCMPE 4v  | FUNE v                     | FEQLE 4v  | FDIV 40v                              | FSQRT 40v | FREM 4v                    | FINT 4v  | # 1 x |  |

| 1 X   | MUL[I] 10v        |           | MULU[I] 10v                |           | DIV[I] 60υ                            |           | DIVU[I] 60v                |          | 1 X   |  |

| #2x   | ADD[I] v          |           | ADDU[I] v                  |           | SUB[I] v                              |           | SUBU                       | [Ι] υ    | # 2x  |  |

| - 2x  | 2ADDU[I] v        |           | 4ADDU[I] v                 |           | 8ADDU[I] v                            |           | 16ADDU[I] v                |          | - ZA  |  |

| #3x   | CMP[I] v          |           | CMPU[I] v                  |           | NEG[I] υ                              |           | NEGU[I] v                  |          | # 3x  |  |

|       | SL[I] v           |           | SLU[I] v                   |           | SR[I] v                               |           | SRU[I] v                   |          | - 3A  |  |

| #4x   | BN                | [B] υ+π   | BZ[B] υ+π                  |           | BP[B] υ+π                             |           | BOD                        | [B] υ+π  | # 4x  |  |

| - 4x  | BNN[B] $v+\pi$    |           | BNZ[B] υ+π                 |           | BNP                                   | [B] υ+π   | BEV                        | [B] υ+π  | - 4x  |  |

| #5x   | PBN               | [B] 3υ-π  | PBZ                        | [B] 3υ-π  | PBP                                   | [B] 3υ-π  | PBOD                       | [B] 3υ-π | #5x   |  |

| " 5 X | PBNN[B] 3υ-π      |           | PBNZ                       | [B] 3υ-π  | PBNP                                  | [B] 3υ-π  | PBEV                       | [B] 3υ-π | - SX  |  |

| #6x   | CSN[I] v          |           | CSZ[I] v                   |           | CSP                                   | [I] v     | CSOD                       | [I] v    | # 6x  |  |

| " O X | CSNN[I] v         |           | CSNZ[I] v                  |           | CSNP[I] v                             |           | CSEV[I] v                  |          | "ox   |  |

| #7x   | ZSN[I] v          |           | ZSZ[I] v                   |           | ZSP[I] v                              |           | ZSOD[I] v                  |          | #7x   |  |

| " / X | ZSNN[I] v         |           | ZSNZ[I] v                  |           | ZSNP[I] v                             |           | ZSEV[I] v                  |          |       |  |

| #8x   | LDB[I] μ+υ        |           | LDBU[I] $\mu+v$            |           | LDW[I] $\mu + v$                      |           | LDWU[I] $\mu + v$          |          | #8x   |  |

| O.X   | LDT[I] $\mu + v$  |           | LDTU[I] $\mu+v$            |           | LDO[I] $\mu + v$                      |           | LDOU[I] $\mu + v$          |          |       |  |

| #9x   | LDSF[I] $\mu + v$ |           | LDHT[I] $\mu+v$            |           | CSWAP[I] $2\mu + 2v$                  |           | LDUNC[I] $\mu + v$         |          | #9x   |  |

| - 9x  | LDVTS[I] v        |           | PRELD[I] v                 |           | PREGO[I] v                            |           | GO[I] 3v                   |          |       |  |

| #Ax   | STB[I] $\mu + v$  |           | $STBU[I]$ $\mu+v$          |           | $\mathtt{STW} \texttt{[I]} \ \mu + v$ |           | STWU[I] $\mu + v$          |          | # Ax  |  |

| АЛ    | STT[I] $\mu + v$  |           | STTU[I] $\mu+v$            |           | STO[I] $\mu + v$                      |           | $\mathtt{STOU[I]}_{\mu+v}$ |          |       |  |

| #Bx   | STSF[I] $\mu + v$ |           | $\mathtt{STHT[I]}_{\mu+v}$ |           | ${\tt STCO[I]}~\mu + v$               |           | STUNC[I] $\mu + v$         |          | #Bx   |  |

| DX    | SYNCD[I] v        |           | PREST[I] v                 |           | SYNCID[I] v                           |           | PUSHGO[I] 3v               |          |       |  |

| #Cx   | OR[I] v           |           | ORN[I] v                   |           | NOR[I] v                              |           | XOR[I] v                   |          | # Cx  |  |

| CX    | AND[I] v          |           | ANDN[I] v                  |           | NAND[I] v                             |           | NXOR[I] v                  |          |       |  |

| #Dx   | BDIF[I] v         |           | WDIF[I] v                  |           | TDIF[I] v                             |           | ODIF[I] v                  |          | #Dx   |  |

| "DX - | MUX[I] v          |           | SADD[I] v                  |           | MOR[I] v                              |           | MXOR[I] v                  |          | DX    |  |

| #Ex   | SETH v            | SETMH $v$ | SETML $v$                  | SETL $v$  | INCH v                                | INCMH v   | ${\tt INCML}\ \upsilon$    | INCL v   | #Ex   |  |

| LA    | ORH $v$           | ORMH v    | ORML $v$                   | ORL v     | ANDNH $v$                             | AND NMH v | ANDNML $v$                 | AND NL v |       |  |

| #Fx   | JMP[B] v          |           | PUSHJ[B] v                 |           | GETA[B] v                             |           | PUT[I] v                   |          | #Fx   |  |

|       | POP 3v            | RESUME 5v | [UN]SA                     | AVE 20μ+υ | SYNC v SWYM v                         |           | GET v                      | TRIP 5v  | 1. Y  |  |

|       | #8                | #9        | # A                        | #B        | # C                                   | # D       | #E                         | # F      |       |  |

$\pi=2v$  if the branch is taken,  $\pi=0$  if the branch is not taken

increases by 1 whenever specified opcodes are executed; and a virtual translation register, rV, which defines a mapping from the "virtual" 64-bit addresses used in programs to the "actual" physical locations of installed memory. These special registers help make MMIX a complete, viable machine that could actually be built and run successfully; but they are not of importance to us in this book. The MMIXware document explains them fully.

## • GETA \$X,RA (get address): $u(\$X) \leftarrow RA$ .

This instruction loads a relative address into register \$X, using the same conventions as the relative addresses in branch commands. For example, GETA \$0,0 will set \$0 to the address of the instruction itself.

Table 2

SPECIAL REGISTERS OF MMIX

|                        | code                                                                                                                                          | e saved? put? |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| rA                     | arithmetic status register                                                                                                                    | ✓ ✓           |

| $_{ m rB}$             | bootstrap register (trip) $\dots \dots \dots$ | ✓ ✓           |

| $^{ m rC}$             | cycle counter                                                                                                                                 |               |

| $^{ m rD}$             | dividend register                                                                                                                             | ✓ ✓           |

| $^{ m rE}$             | epsilon register                                                                                                                              | ✓ ✓           |

| rF                     | failure location register                                                                                                                     | $\checkmark$  |

| rG                     | global threshold register                                                                                                                     | ✓ ✓           |

| $_{ m rH}$             | himult register                                                                                                                               | ✓ ✓           |

| $_{ m rI}$             | interval counter                                                                                                                              |               |

| $_{ m rJ}$             | return-jump register 4                                                                                                                        | ✓ ✓           |

| rK                     | interrupt mask register                                                                                                                       |               |

| rL                     | local threshold register                                                                                                                      | ✓ ✓           |

| rM                     | multiplex mask register 5                                                                                                                     | ✓ ✓           |

| rN                     | serial number                                                                                                                                 |               |

| $_{ m rO}$             | $register\ stack\ offset  .  .  .  .  .  .  .  .  .  $                                                                                        |               |

| $^{ m rP}$             | prediction register                                                                                                                           | ✓ ✓           |

| rQ                     | interrupt request register                                                                                                                    |               |

| $_{ m rR}$             | remainder register 6                                                                                                                          | ✓ ✓           |

| rS                     | register stack pointer                                                                                                                        |               |

| m rT                   | trap address register                                                                                                                         |               |

| $\mathrm{rU}$          | usage counter                                                                                                                                 |               |

| ${ m rV}$              | virtual translation register                                                                                                                  |               |

| ${ m rW}$              | where-interrupted register (trip) 24                                                                                                          | ✓ ✓           |

| $_{\mathrm{rX}}$       | execution register (trip) $\dots \dots \dots$ | ✓ ✓           |

| $\mathbf{r}\mathbf{Y}$ | Y operand (trip)                                                                                                                              | ✓ ✓           |

| rZ                     | Z operand (trip)                                                                                                                              | ✓ ✓           |

| rBB                    | bootstrap register (trap)                                                                                                                     | $\checkmark$  |

| rTT                    | dynamic trap address register                                                                                                                 |               |

| rWW                    | where-interrupted register (trap)                                                                                                             | $\checkmark$  |

| rXX                    | execution register (trap)                                                                                                                     | $\checkmark$  |

| rYY                    | Y operand (trap)                                                                                                                              | $\checkmark$  |

| rZZ                    | Z operand (trap)                                                                                                                              | $\checkmark$  |

• SWYM X,Y,Z or SWYM X,YZ or SWYM XYZ (sympathize with your machinery). The last of MMIX's 256 opcodes is, fortunately, the simplest of all. In fact, it is often called a no-op, because it performs no operation. It does, however, keep the machine running smoothly, just as real-world swimming helps to keep programmers healthy. Bytes X, Y, and Z are ignored.

Timing. In later parts of this book we will often want to compare different MMIX programs to see which is faster. Such comparisons aren't easy to make, in general, because the MMIX architecture can be implemented in many different ways. Although MMIX is a mythical machine, its mythical hardware exists in cheap, slow versions as well as in costly high-performance models. The running time of a program depends not only on the clock rate but also on the number of

functional units that can be active simultaneously and the degree to which they are pipelined; it depends on the techniques used to prefetch instructions before they are executed; it depends on the size of the random-access memory that is used to give the illusion of  $2^{64}$  virtual bytes; and it depends on the sizes and allocation strategies of caches and other buffers, etc., etc.